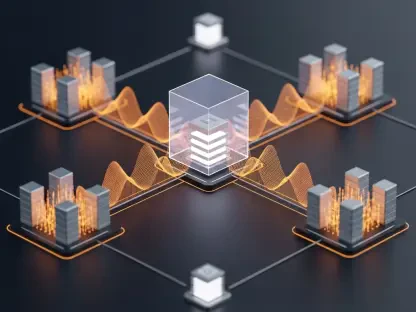

Supply lines that once flowed predictably have been jolted by AI’s appetite for parallel compute, pulling wafer starts, advanced packaging capacity, and top-tier memory toward accelerators while leaving CPUs to fight for space in the same fabs. The result is a new hierarchy: GPUs first, HBM close behind, and CPUs recast as orchestration engines with limited but strategic shares of cutting-edge nodes.

This power shift runs through an ecosystem defined by PCIe, CXL, and DDR/HBM pairings, along with software frameworks that favor accelerator-rich topologies. Intel, AMD, Nvidia, TSMC, and Samsung are all repositioning inside this map, yet scarcity has created a narrow path for CPU vendors: extend binning deeper into the yield tail, segment cleanly, and monetize dies that would have been scrap when supply was loose.

From Scarcity to Strategy: How AI Demand Rewired the CPU Market

Demand Whiplash—GPU Crunch Spills Over, Elevating CPU Roles

GPU shortages cascaded into memory and storage, then circled back to CPUs, which suddenly mattered more for scheduling, pre/post-processing, data marshaling, security, and IO arbitration. As clusters scaled, the CPU’s role expanded from background utility to conductor, coordinating accelerator fleets and handling non-parallel work that cannot be offloaded.

Buyers adjusted quickly. Availability trumped perfection, and “good enough” became acceptable for edge nodes, batch inference, or cost-bound deployments. Intel pivoted by packaging borderline dies as budget SKUs, backing them with conservative clocks, firmware tuning, and explicit guardrails to preserve reliability even as headline performance narrowed.

By the Numbers—Revenue Beats, ASP Inflation, and Forward Indicators

Intel reported Q1 2026 revenue of $13.6B versus $12.36B expected, with server CPU ASPs up 27% and 16% of data center growth tied to price. Salvaging lower bins lifted unit volume while rising ASPs expanded margin, creating a dual tailwind rare in mature CPU cycles.

Operational signals echoed the shift: longer lead times, denser SKU stacks, and normalized heterogeneity across fleets. Forecasts pointed to sustained AI buildouts, with mix moving from training-centric phases toward inference and agentic operations that distribute work more evenly across CPUs and accelerators.

Operational Trade-Offs, Yield Realities, and Market Frictions

Lower-binned CPUs satisfy reliability specs but carry tighter frequency and power envelopes, which can translate into higher energy per unit of work. In hyperscale estates, that penalty compounds, arguing for careful placement in roles where power sensitivity is secondary to availability and cost.

Clarity becomes a competitive asset. Tight segmentation, transparent benchmarks, and unambiguous TDP and turbo behavior reduce confusion and protect brand trust. Even so, monetizing the yield tail does not create new wafers; durable relief still hinges on node ramps and packaging scale that balance GPU and CPU allocation.

Rules of the Road—Compliance, Security, and Standards That Matter

Export controls and regional trade policies continue to steer where advanced CPUs and GPUs can land, shaping SKU menus by geography. Product labeling, burn-in criteria, and warranty practices for low-tier parts must be explicit to align expectations and limit returns.

Data center guardrails—secure boot chains, microcode management, and compliance reporting—remain table stakes, particularly as fleets diversify. Interface choices like CXL over DDR5 and PCIe Gen5/Gen6 bandwidths define viable pairings, ensuring lower-tier chips still meet the IO and memory footprints their roles demand.

The Road Ahead—Heterogeneous Compute, Capacity Bets, and New Economics

Heterogeneity looks durable: CPUs handle orchestration and IO, accelerators drive parallel kernels, and domain-specific silicon proliferates at the edge. Expect finer-grained SKUs and adaptive pricing as software schedulers improve workload placement across mixed-performance pools.

On supply, the arc runs through node transitions, chiplet partitioning, and 2.5D/3D packaging that reuse known-good die across product tiers. Disruptors—ARM servers, custom silicon, RISC-V niches, efficiency-first designs—could reshape TCO math, while capital intensity, rates, incentives, and sustainability targets govern the tempo of data center growth.

Final Take—Pragmatic Monetization Today, Optionality for Tomorrow

The evidence showed Intel extracting value from the yield tail just as AI scarcity lifted unit demand and prices, with quality bands enforced and roles clearly scoped. Buyers who modeled power-performance curves, prioritized transparent specs, and routed workloads by latency and efficiency sensitivity made smarter trade-offs under constraint.

Vendors that kept SKU discipline, validated aggressively, and invested in heterogenous fleet tooling sustained trust while widening choice. Near term gains depended on pricing power and salvage strategy; medium-term outcomes hinged on capacity adds, packaging scale, and competitive countermoves. The practice remained likely to persist through the AI buildout, shaping product tiers and software assumptions until supply and pricing finally rebalanced.